26/01/2026

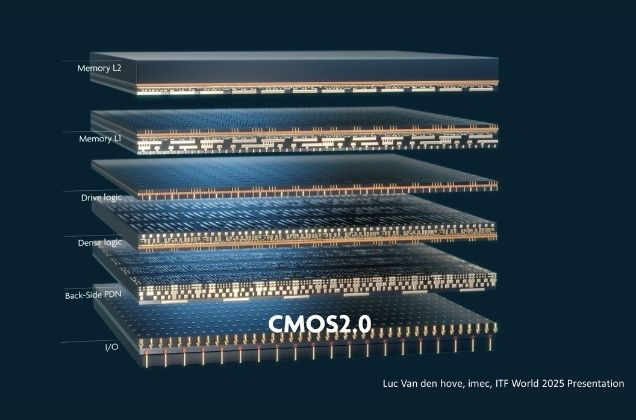

CMOS teknolojisi, yarıiletken chip üretimi için performans, enerji verimliliği ve fiyat unsurlarını dengeleyerek elektronik endüstrisinde devrim yarattı. Ancak CMOS teknolojisinin bugün fiziksel sınırlarına yaklaşmakta olduğu birçok kişi tarafından kabul ediliyor. CMOS 2.0'da tam bu noktada yeni bir paradigma olarak işlevlerin çoklu 3 boyutlu (3D) istiflenmiş katmanlarda özel çipler sayesinde tasarlanmasını hedeflemektedir. CMOS 2.0 yaklaşımı 3D entegrasyon teknolojilerini kullanmakla beraber yüksek iletişim hassasiyeti ve paket içi yüksek teknoloji heterojenliği sayesinde geleneksel CMOS'un kısıtlamalarını ortadan kaldırabilecektir.

Geçtiğimiz günlerde, CMOS 2.0 teknolojisi üzerine birlikte araştırma yapmak üzere Sabancı Üniversitesi ile Belçika’nın önde gelen nanoelektronik ve dijital teknolojiler alanlarında faaliyet gösteren uluslararası araştırma ve geliştirme kuruluşu IMEC arasında toplam 384.000 EUR bütçeli iki yeni proje anlaşması imzalandı. Bu kapsamda birbiriyle ilintili iki ayrı tema üzerinde ortak araştırmalar yapılması, doktora ve yüksek lisans öğrencileri ile birlikte çalışılması hedefleniyor.

“Reconfigurable Architectures Using Non-Volatile Memory on CMOS 2.0 Fabrics” başlıklı proje, çok katmanlı heterojen CMOS 2.0 mimarilerinde verimli yeniden yapılandırılabilir sistem mimarileri oluşturmak için mekanizmalar geliştirmeyi amaçlamaktadır. Geleneksel 3D tasarım ve üretim teknolojileri yirmi yılı aşkın süredir mevcut olmasına rağmen, yeniden yapılandırılabilir mimari ortamındaki uygulamaları nispeten sınırlı kalmıştır. Yoğun 3D (çok katmanlı) heterojen CMOS 2.0 mimarilerinin sunduğu yeteneklerin yeni fırsatlar getirmesi beklenmektedir.

Bu araştırmadaki amacımız, CMOS 2.0 bağlamında kalıcı bellekler kullanarak çok katmanlı yeniden yapılandırılabilir mimarileri incelemektir. Klasik entegre uygulamalarının aksine, 3 boyutlu tasarımların kullanımıyla verimli fonksiyon dağılımı ve hücre kullanımı oluşturmak mümkündür. Bu tür bir 3 boyutlu hacimde, bölümlendirme, yerleşim planlaması, yerleştirme ve yönlendirme açısından çok daha fazla esneklik elde etmek mümkündür. Dikey entegrasyon ve kalıcı bellek blokları yardımıyla yeniden yapılandırılabilir tasarımların optimize edilebilmesi mümkün olacaktır.

Yarıiletken dünyasında 2D düzlemsel mimarilerden çok katmanlı (multi-tier) SoC “fabrics” yaklaşımına geçiş; performans, yoğunluk ve fonksiyonellik açısından büyük kazanımlar sunarken, aynı zamanda katmanlar arası veri iletişimini (yatay, dikey TSV tabanlı ve hibrit bağlantılar) kritik bir darboğaz hâline getiriyor. Bu nedenle CMOS 2.0 bağlamında, yüksek yoğunluklu 3D yapılarda veri hızı–güç verimliliği–alan ve hacim kullanımının aynı anda optimize edilmesini sağlayacak yeni sinyal alma ve gönderme metotları, sistemleri ve devre tasarımlarına ihtiyaç duyuluyor.

“Investigation of Signaling Methods within CMOS 2.0 Architectures” başlıklı diğer projemizde, CMOS 2.0 çok katmanlı SoC mimarilerinde veri iletişimi için en uygun sinyal iletişim yöntemlerini sistematik biçimde karşılaştırmayı ve optimize etmeyi hedefliyoruz. Bu projemiz kapsamında, paralel/seri veri yolu mimarileri, NRZ/PAM-n/m-ary QAM gibi modülasyon seçenekleri ile full-swing/low-swing ve single-ended/differential (LVDS) gibi iletim yaklaşımları; ayrıca yüksek yoğunluklu dikey TSV’lerin elektriksel ve termal etkileri birlikte değerlendirilecektir. Çalışmanın çıktıları güç–hız–yoğunluk etkileşimlerinin nicel analizi, yatay/dikey test yapılarının tasarım ve modellenmesi, seçilen mimarilerin yerleşim ve fiziksel testini içeren donanım prototipleri ve EDA 2.0 araçları için tasarım kılavuzları olarak öngörmekteyiz.

IMEC tarafından desteklenen CMOS 2.0 projeleri, Mühendislik ve Doğa Bilimleri Fakütesi öğretim üyelerimiz Özcan Öztürk ve Korkut Kaan Tokgöz tarafından yönetilecektir.